芯片,作为现代电子设备的 “大脑”,其大小仅相当于指甲盖,内部却集成了数十亿甚至上万亿个纳米级晶体管。这一精密器件的制造过程,堪称人类工业文明的巅峰之作 —— 需历经上百道工序、跨越物理与化学的多重边界,从高纯度硅料到复杂电路,每一步都充满 “技术魔法”。深入拆解芯片制造流程,不仅能读懂科技产品的核心密码,更能理解全球半导体产业竞争的关键所在。

芯片,作为现代电子设备的 “大脑”,其大小仅相当于指甲盖,内部却集成了数十亿甚至上万亿个纳米级晶体管。这一精密器件的制造过程,堪称人类工业文明的巅峰之作 —— 需历经上百道工序、跨越物理与化学的多重边界,从高纯度硅料到复杂电路,每一步都充满 “技术魔法”。深入拆解芯片制造流程,不仅能读懂科技产品的核心密码,更能理解全球半导体产业竞争的关键所在。

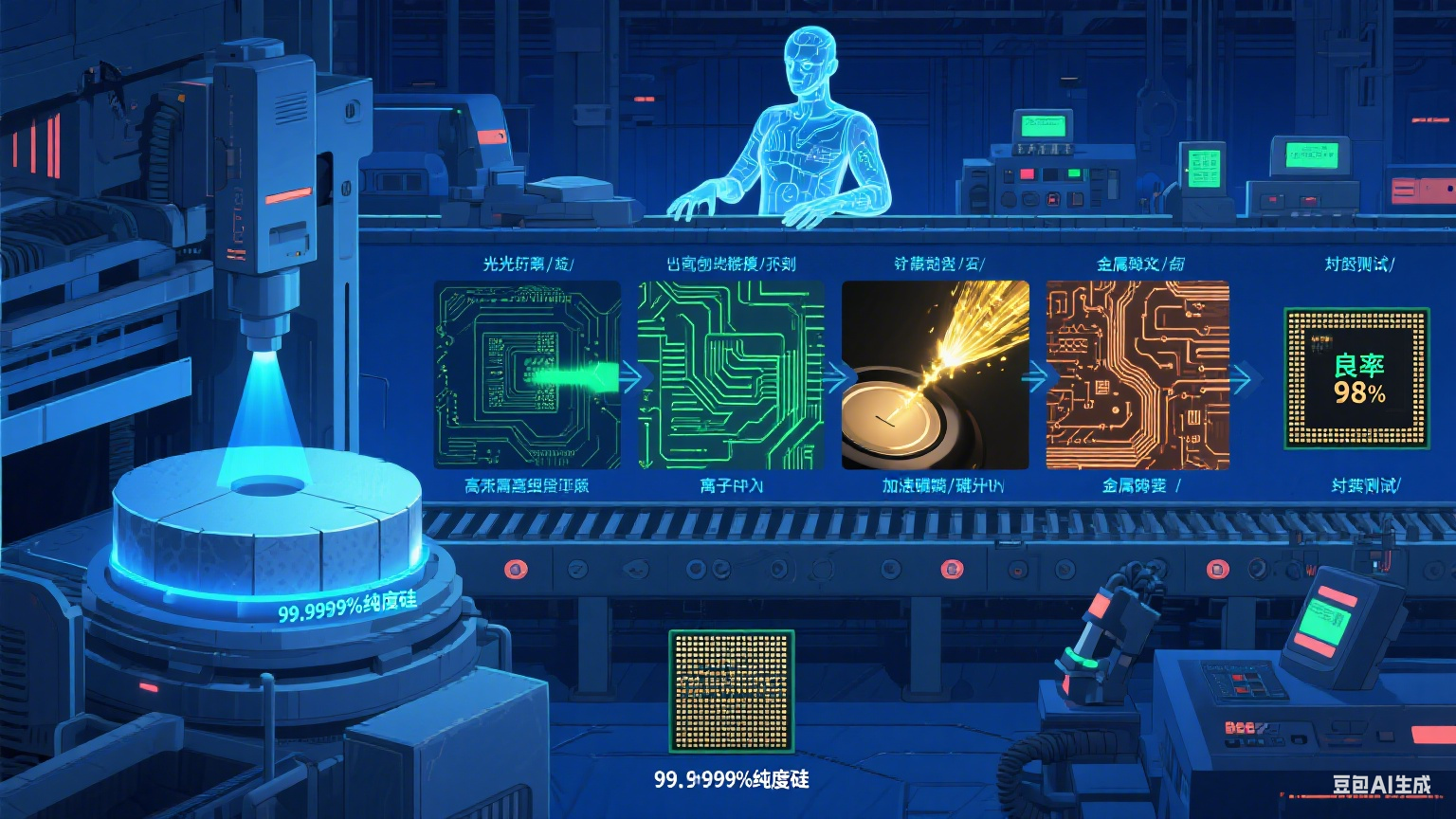

芯片制造的起点,是看似普通却纯度极高的硅片。地壳中硅元素含量高达 28%,但天然硅多以二氧化硅(如石英砂)形式存在,需经过多轮提纯与加工,才能成为符合芯片要求的 “基底材料”。

硅片制备首先从 “硅提纯” 开始:将石英砂与焦炭在高温电弧炉中反应,生成纯度约 98% 的工业硅;随后通过 “西门子法” 进一步提纯 —— 将工业硅制成三氯氢硅气体,再通过高温还原反应生成高纯度多晶硅,纯度可达 99.999999999%(11 个 9),堪称 “地球上最纯净的物质之一”。这种高纯度多晶硅外观呈银灰色,质地脆硬,需经过 “单晶生长” 转化为单晶硅:将多晶硅放入石英坩埚,在 1420℃高温下熔化成硅液,再插入籽晶(单晶硅晶种),以每分钟几毫米的速度缓慢提拉,使硅原子沿籽晶结构有序排列,形成圆柱形的单晶硅棒。单晶硅棒的直径决定了硅片尺寸,目前主流尺寸为 12 英寸(300 毫米),相比 8 英寸硅片,12 英寸硅片可切割出更多芯片,大幅降低单位成本。

最后一步是 “硅片切割与抛光”:用金刚石锯将单晶硅棒切割成厚度仅 0.7-1.2 毫米的圆形硅片,再通过多轮机械抛光与化学腐蚀,去除表面划痕与杂质,使硅片表面平整度控制在纳米级(误差不超过 1 纳米)—— 相当于在 1 公里的道路上,高低差不超过 1 毫米。抛光后的硅片表面如镜面般光滑,可用于后续电路制作,此时的硅片也被称为 “晶圆”,是芯片制造的核心载体。

如果说硅片是芯片的 “画布”,那么光刻技术就是 “画笔”,其作用是将设计好的电路图案转移到晶圆表面,是芯片制造中最关键、最复杂的工序,也是决定芯片制程(如 7 纳米、3 纳米)的核心技术。

光刻的第一步是 “涂胶”:在晶圆表面均匀涂抹一层光刻胶(一种对紫外线或深紫外光敏感的感光材料),涂胶厚度需精确控制在几十纳米,且表面无气泡、无颗粒 —— 任何微小杂质都可能导致后续电路缺陷。涂胶后的晶圆需经过预烘烤,去除光刻胶中的溶剂,增强其与晶圆的附着力。

接下来是 “曝光”:将光刻掩模版(印有电路图案的透明石英板)与晶圆精准对齐(对齐误差需小于 1 纳米),再用高能量光源(如深紫外光 DUV、极紫外光 EUV)照射掩模版。光线透过掩模版上的电路图案,投射到晶圆表面的光刻胶上,使光刻胶发生化学变化 —— 正性光刻胶被光照区域会溶解,负性光刻胶则相反。目前最先进的 EUV 光刻技术,采用波长仅 13.5 纳米的极紫外光,可在晶圆上绘制出 3 纳米甚至 2 纳米的电路图案,但其设备造价高达 1.5 亿美元,全球仅荷兰 ASML 公司能量产,是半导体产业的 “卡脖子” 设备之一。

曝光完成后,需进行 “显影”:用显影液冲洗晶圆,去除光刻胶中被光照(或未被光照)的部分,使电路图案清晰地呈现在晶圆表面。显影后的晶圆需再次烘烤,固化剩余的光刻胶,为后续蚀刻工序做准备。值得注意的是,先进制程芯片(如 7 纳米以下)需经过多次光刻与蚀刻(即 “多重曝光”),通过叠加不同的电路图案,才能实现更小的晶体管尺寸,工序复杂度呈指数级增长。

光刻完成后,晶圆表面仅留下光刻胶形成的 “电路图案保护层”,还需通过蚀刻去除多余的硅材料,再通过掺杂改变硅的导电性,才能形成真正的晶体管与电路。

“蚀刻” 的原理类似 “雕刻”:将晶圆放入蚀刻机中,通入腐蚀性气体(如氟化物气体)或使用等离子体,对未被光刻胶保护的硅材料进行腐蚀。干法蚀刻(等离子体蚀刻)是目前主流技术,其精度可达纳米级,能精准控制蚀刻深度与形状 —— 例如,在制作晶体管的 “沟道” 时,蚀刻深度需控制在 10 纳米以内,误差不能超过 1 纳米。蚀刻完成后,需用溶剂去除残留的光刻胶,此时晶圆表面已形成凹陷的电路沟槽与凸起的电路线条,电路图案从 “蓝图” 变为 “立体结构”。

“掺杂” 则是改变硅导电性的关键步骤,目的是在硅材料中形成 N 型(富含电子)和 P 型(缺乏电子)半导体区域,从而构成晶体管的源极、漏极与栅极。掺杂主要采用 “离子注入” 技术:将杂质离子(如磷离子、硼离子)加速到极高速度,注入到晶圆表面的特定区域(通过光刻胶遮挡实现精准定位)。注入的杂质离子会改变硅的电子结构 —— 注入磷离子形成 N 型半导体,注入硼离子形成 P 型半导体。注入完成后,需进行 “退火” 处理:将晶圆加热到 1000℃左右,使杂质离子在硅中均匀扩散,同时修复离子注入造成的硅晶格损伤,增强半导体的稳定性。

通过蚀刻与掺杂的反复配合,晶圆表面会形成数十亿个晶体管:每个晶体管由源极(电子流出端)、漏极(电子流入端)、栅极(控制电子流动的 “开关”)组成,栅极的长度就是芯片的制程(如 7 纳米制程即指栅极长度为 7 纳米)。晶体管的密度直接决定芯片性能 ——3 纳米制程芯片每平方毫米可集成约 1.5 亿个晶体管,是 7 纳米制程的 2 倍以上,能实现更快的运算速度与更低的功耗。

单个晶体管无法实现运算功能,需通过金属互联形成电路,再经过封装保护,才能成为可使用的芯片。

“金属互联” 的核心是在晶体管之间铺设金属导线(通常为铜或铝),实现信号与电力的传输。首先在晶圆表面沉积一层绝缘层(如二氧化硅),再通过光刻与蚀刻在绝缘层上开出 “通孔”,然后采用 “电镀” 技术在通孔与表面铺设金属层,形成金属导线。先进制程芯片需铺设多层金属互联(如 7 纳米芯片需 10-12 层),层与层之间通过通孔连接,形成三维电路网络。金属导线的宽度与间距需控制在纳米级,例如 3 纳米芯片的金属导线宽度仅 20 纳米左右,任何短路或断路都会导致芯片失效,因此金属互联的良率控制是芯片制造的重要挑战。

金属互联完成后,晶圆需经过 “测试与切割”:先对晶圆上的每个芯片(称为 “裸片”)进行电学测试,筛选出合格裸片;再用金刚石刀具将晶圆切割成独立的裸片,不合格的裸片则被剔除。最后一步是 “封装”:将合格裸片固定在封装基板上,通过金线或铜线将裸片的电极与封装基板的引脚连接,再用环氧树脂等材料封装保护,防止裸片受外界环境(如湿度、温度、灰尘)影响。封装后的芯片还需进行最终测试,确保其电学性能、稳定性符合要求,才能出厂用于手机、电脑、汽车等电子设备。

从高纯度硅料到纳米级电路,芯片制造历经上百道工序,涉及材料科学、精密机械、光学工程等多个学科,是全球产业链协同的产物 —— 例如,硅片可能来自日本信越化学,光刻胶来自韩国东进化学,光刻设备来自荷兰 ASML,封装测试可能在中国台湾地区完成。理解这一 “魔法之旅”,不仅能感受人类科技的极致精度,更能认识到半导体产业自主可控的重要性。随着制程技术不断突破(如 2 纳米、1 纳米),芯片制造的 “魔法” 还将持续升级,推动人类社会向更智能、更高效的未来迈进。

版权声明:本文为 “联成科技技术有限公司” 原创文章,转载请附上原文出处链接及本声明;